|

|

|

|

Hello Forum,

I'm having a problem coping with this....the RAM8 chip has an address [3] as an input parameter which is fine as DMux will identify a channel 0...7. What I don't understand though is how one can bind a particular register to the channel, since the registers themselves don't appear to have an identifier. I know that I'm probably misunderstanding here. I'd like to clear this up or else I risk progressing without a fundamental appreciation.

Any help really welcome.

Thanks

John Savage

|

|

Administrator

|

savage wrote

Hello Forum,

I'm having a problem coping with this....the RAM8 chip has an address [3] as an input parameter which is fine as DMux will identify a channel 0...7. What I don't understand though is how one can bind a particular register to the channel, since the registers themselves don't appear to have an identifier. I know that I'm probably misunderstanding here. I'd like to clear this up or else I risk progressing without a fundamental appreciation.

Any help really welcome.

Thanks

John Savage

The Registers do, in a way, have something unique that that identifies them: the name of the wire (bus, actually) connected to their out pin.

Register(..., out=r0out);

Register(..., out=r1out);

etc.

address needs to control which of the r?out get routed to the RAM8 out.

Similarly, it needs to control the load input of the individual Registers.

Do Registers care what their input is if they are not being loaded?

--Mark

|

|

|

Hello Mark,

Thank you for replying so quickly. Ill got work on your info and let you know how I get on.

John Savage

|

|

|

Hello again Mark,

To paraphrase Dr Doolittle: "By George he's got it! I think he's got it"

I see what you mean by the output label on a register being the key to its address.

And yes, it doesn't matter if you present an input to a register if you have no intention of loading it (or not) into that register.

Well - on to the next step now.

Many thanks

John Savage

|

|

|

cadet1620 wrote

<snip>

address needs to control which of the r?out get routed to the RAM8 out.

Similarly, it needs to control the load input of the individual Registers.

Do Registers care what their input is if they are not being loaded?

--Mark

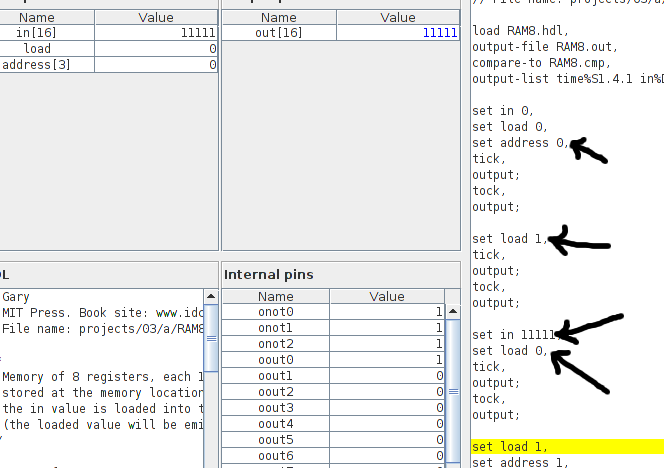

I ended up using a DMux8Way for the address decoding to get the RAM8 to work  . I had trying using :

Not(in=address[0], out=onot0);

Not(in=address[1], out=onot1);

Not(in=address[2], out=onot2);

And3(a=onot2, b=onot1, c=onot0, out=oout0);

And3(a=onot2, b=onot1, c=address[0], out=oout1);

And3(a=onot2, b=address[1], c=onot0, out=oout2);

And3(a=onot2, b=address[1], c=address[0], out=oout3);

And3(a=address[2], b=onot1, c=onot0, out=oout4);

And3(a=address[2], b=onot1, c=address[0], out=oout5);

And3(a=address[2], b=address[1], c=onot0, out=oout6);

And3(a=address[2], b=address[1], c=address[0], out=oout7);

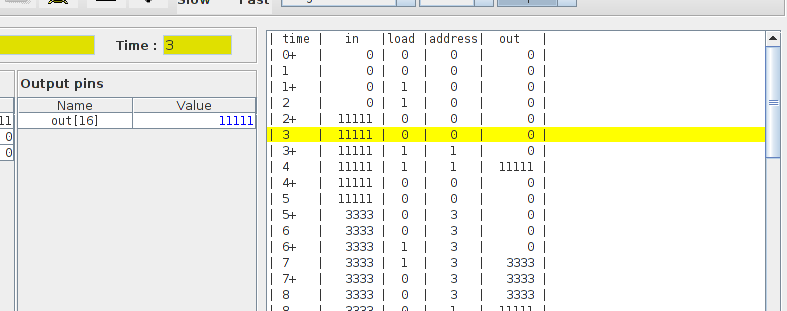

I'm not quite clear, what I can't use the above. One difference is the above will assert a 1 at one of the addresses, whereas the DMux8Way also does this, but also asserts 0's at the other addresses.

I was curious why the above addressing (Not/And) does not work, and are they used for other types of memory systems?  Below is a snapshot with my And/Not addressing scheme. It seems to load 11111 into Register 0 (address 0) and then when the load 0 toggles, it dumps that 111111 to the output. Is this some sort of timing problem? The compare file expects a 0 on the output at this point and not 11111. Here are the snapshots:

|

|

Administrator

|

linuxford wrote

Not(in=address[0], out=onot0);

Not(in=address[1], out=onot1);

Not(in=address[2], out=onot2);

And3(a=onot2, b=onot1, c=onot0, out=oout0);

And3(a=onot2, b=onot1, c=address[0], out=oout1);

And3(a=onot2, b=address[1], c=onot0, out=oout2);

And3(a=onot2, b=address[1], c=address[0], out=oout3);

And3(a=address[2], b=onot1, c=onot0, out=oout4);

And3(a=address[2], b=onot1, c=address[0], out=oout5);

And3(a=address[2], b=address[1], c=onot0, out=oout6);

And3(a=address[2], b=address[1], c=address[0], out=oout7);

This is the canonical representation of a 3-to-8 decoder, and is functionally the same as:

DMux8Way(sel=address, in=true, a=oout0, b=oout1, ..., h=oout7);

The screen shot is showing the compare file so I can't see what's happening with your circuit, but assuming that the highlighted line is the failure location, it looks like you had oout0 tied directly to the register's load input so the register was continuously loading while it was addressed, ignoring the RAM8's load.

--Mark

|

|

|

cadet1620 wrote

linuxford wrote

Not(in=address[0], out=onot0);

Not(in=address[1], out=onot1);

Not(in=address[2], out=onot2);

And3(a=onot2, b=onot1, c=onot0, out=oout0);

And3(a=onot2, b=onot1, c=address[0], out=oout1);

And3(a=onot2, b=address[1], c=onot0, out=oout2);

And3(a=onot2, b=address[1], c=address[0], out=oout3);

And3(a=address[2], b=onot1, c=onot0, out=oout4);

And3(a=address[2], b=onot1, c=address[0], out=oout5);

And3(a=address[2], b=address[1], c=onot0, out=oout6);

And3(a=address[2], b=address[1], c=address[0], out=oout7);

This is the canonical representation of a 3-to-8 decoder, and is functionally the same as:

DMux8Way(sel=address, in=true, a=oout0, b=oout1, ..., h=oout7);

The screen shot is showing the compare file so I can't see what's happening with your circuit, but assuming that the highlighted line is the failure location, it looks like you had oout0 tied directly to the register's load input so the register was continuously loading while it was addressed, ignoring the RAM8's load.

--Mark

Awesome Mark!!  That is exactly what I was doing  Beautiful. Great. I think I understand now. Great feeling when you are stumped and confused to get an expert insight that is understandable. Thanks very much.

So to correct it, I went ahead and built and used an And4 and Anded the 3 bit address with the load bit, and it compared fine with the Canonical version.

And4(a=onot2, b=onot1, c=onot0, d=load, out=oout0)

Register(in=in, load=oout0, out=rout0);

|

|