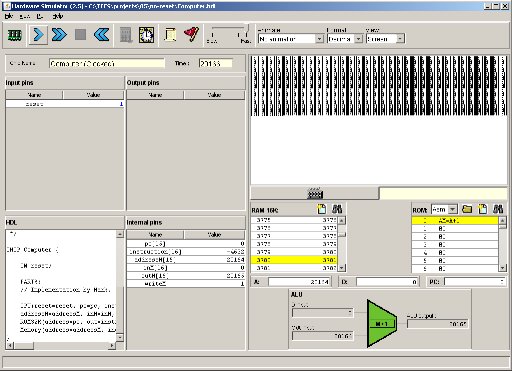

Yes, that's the problem. The instruction at 0 executes repeatedly during reset. You can watch this happen in the Hardware Simulator by loading AM=A+1 into RAM[0], setting

reset=1, and letting it run. It will eventually write a counting pattern to the screen.

You don't need to specifically add

reset to individual control signals; it's better to have master signals

aInst and

cInst (you may already have these if you didn't use

instruction[15] directly). Then these signals can be anded with

reset and all the other control signals will behave correctly.

--Mark