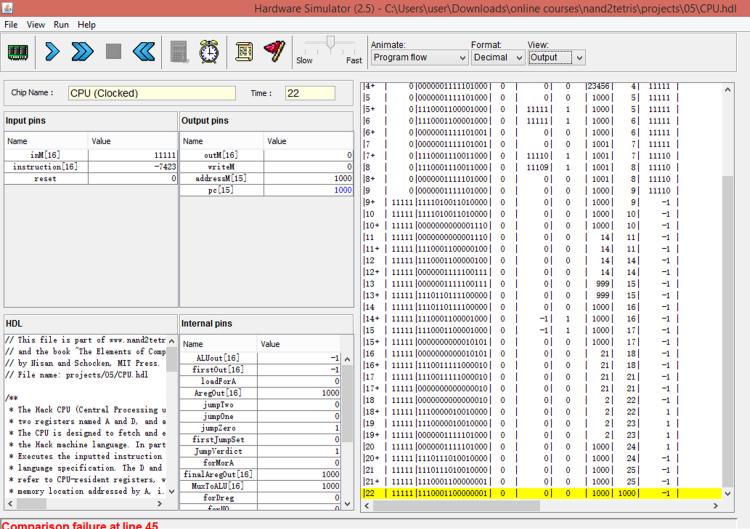

My c-instruction at the highlighted part has '001' for the last three digits. We have agreed that as long as there is no jump, the PC will increment by 1. Yet the correct value is supposed to be 26 for the PC counter, not 1000, which is the value of A-reg. But instruction[16] does have a jump (001 is JGT). Please help me out. Thanks.