Hi, everyone,

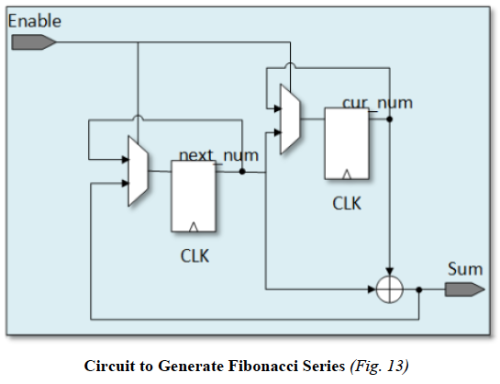

I'm thinking about how to make a fibonacci sequence generator with two Registers. While I'm working on it, I doubt if it is feasible here because I'm stuck somewhere which will be described. Here is the basic circuit I used for this purpose.

The initial two inputs are two numbers f0 and f1, and they are connected to the next_num and cur_num, respectively. The first register is basically the most left mux and the flip flop and the second register is the right mux and the neighboring flip flop.

Assuming my Register stores 4-bit long numbers, so, obviously, we will have this:

Register4(in=sum, load=enable, out=next_num);

But if I do this, what should I do with the input f0? I don't know how to set f0 to next_num as the initial value. Similarly, I'm not sure how to deal with the cur_num and the f1.

Any thoughts for this?