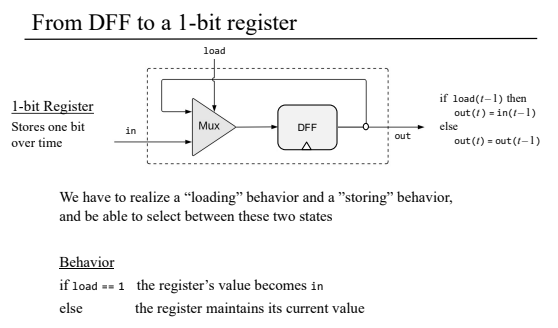

In chapter 3, we use a mux and a dff to implement a 1 bit register. Looking at the schematics, it seems the circuit is recursive,

IIUC, the input to the mux is the output of DFF, and the input to the DFF is the output of mux. Which one is initialized first and with what value?

I will guess and assume it is the DFF at 0+ time with value 0. After which the circuit can move on to evaluating the mux gate and again the DFF gate. Such that at 't = 1' we get the output of whole 1 bit register. Is my understanding correct? i.e. the whole 1 bit register is evaluated within the 1 clock cycle (tick and tock).

The other question: if DFF out at t=0 is not know in real world, how does the mux gate ever get evaluated? Does it not require the out value from DFF to be evaluated successfully?