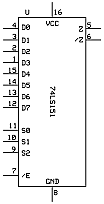

Industrial schematics usually use a symbol like this for multiplexers. (In this case, an 8-to-1 mux.)

When a "shape" symbol is used, it is usually a trapezoid. The

sel can be on either top or bottom. The

a or

D0 input is usually at the top. The inputs are often labeled to avoid confusion. For wider than 2-to-1 muxes, it is common to only label the

a or

D0 input. This is the TECS Mux8Way16 symbol I use. The '/' indicates a bus and its width.

--Mark