Hi all,

I am trying to implement CPU.hdl and when I run my solution with this line.

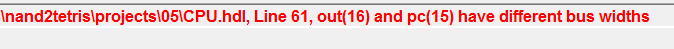

PC(in=AandM, load=jump, inc=true, reset=reset, out=pc);

I get the following error message.

The input AndM is coming from built-in ARegister and it is 16 bits.

Can someone please point out to me my mistake.

Thanks.