Special XOR for half-adder and full-adder

Posted by jonk on

URL: http://nand2tetris-questions-and-answers-forum.52.s1.nabble.com/Special-XOR-for-half-adder-and-full-adder-tp4029600.html

I'm considering the idea of using a special kind of XOR based entirely on NAND, but which provides two outputs: the usual XOR output and a special output which is the inverted carry. This could be used to then form a half adder and full adder.

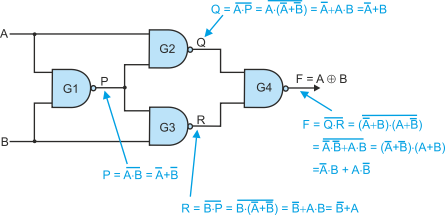

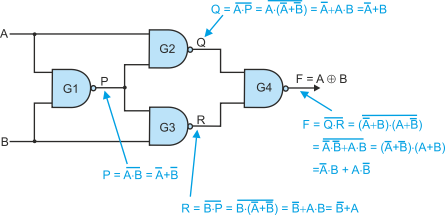

The NAND structure is the usual one for XOR, using four NANDs:

In this case, I'd like to also output the "P" value output of G1 shown in the diagram as the NCARRY (or negated carry bit.)

The trouble I'm having is in wiring up P to the chip output AND also wiring it into the inputs of G2 and G3. I'm getting an error even though there is no unstable loop formed by the use of an output chip pin as inputs to G2 and G3 (which then drive G4.)

How can I achieve something like this:

CHIP XorS {

IN a, b;

OUT sum, ncarry;

PARTS:

Nand( a=a, b=b, out=ncarry );

Nand( a=a, b=ncarry, out=q );

Nand( a=ncarry, b=b, out=r );

Nand( a=q, b=r, out=sum );

}

I get an error with the above. Is there a way to specify an internal "wire" that I can then "tie" to ncarry? Something like:

CHIP XorS {

IN a, b;

OUT sum, ncarry;

PARTS:

Nand( a=a, b=b, out=p );

Nand( a=a, b=p, out=q );

Nand( a=p, b=b, out=r );

Nand( a=q, b=r, out=sum );

ncarry=p;

}

I'm just stuck on this one for now.

Thanks in advance,

Jon

URL: http://nand2tetris-questions-and-answers-forum.52.s1.nabble.com/Special-XOR-for-half-adder-and-full-adder-tp4029600.html

I'm considering the idea of using a special kind of XOR based entirely on NAND, but which provides two outputs: the usual XOR output and a special output which is the inverted carry. This could be used to then form a half adder and full adder.

The NAND structure is the usual one for XOR, using four NANDs:

In this case, I'd like to also output the "P" value output of G1 shown in the diagram as the NCARRY (or negated carry bit.)

The trouble I'm having is in wiring up P to the chip output AND also wiring it into the inputs of G2 and G3. I'm getting an error even though there is no unstable loop formed by the use of an output chip pin as inputs to G2 and G3 (which then drive G4.)

How can I achieve something like this:

CHIP XorS {

IN a, b;

OUT sum, ncarry;

PARTS:

Nand( a=a, b=b, out=ncarry );

Nand( a=a, b=ncarry, out=q );

Nand( a=ncarry, b=b, out=r );

Nand( a=q, b=r, out=sum );

}

I get an error with the above. Is there a way to specify an internal "wire" that I can then "tie" to ncarry? Something like:

CHIP XorS {

IN a, b;

OUT sum, ncarry;

PARTS:

Nand( a=a, b=b, out=p );

Nand( a=a, b=p, out=q );

Nand( a=p, b=b, out=r );

Nand( a=q, b=r, out=sum );

ncarry=p;

}

I'm just stuck on this one for now.

Thanks in advance,

Jon

| Free forum by Nabble | Edit this page |