|

|

|

|

This post was updated on .

Just curious.

Edit: Or if the question is easier to answer: how many physical NAND gates would be required in a physical implementation of the whole computer?

|

|

Administrator

|

The total size of the Hack Computer is primarily for the memory requirement: 256 Kbits for RAM, 128 Kbits for Screen and 512 Kbits for ROM.

The CPU can be done in 1160 2-input Nand gates. In CMOS, each Nand requires 4 transistors.

An actual CMOS implementation could take advantage of other logical gate types, and transmission gates, to substantially reduce the transistor count.

--Mark

|

|

|

Awesome, thanks for the info.

On 3 Jul 2016 20:42, "cadet1620 [via Nand2Tetris Questions and Answers Forum]" < [hidden email]> wrote:

The total size of the Hack Computer is primarily for the memory requirement: 256 Kbits for RAM, 128 Kbits for Screen and 512 Kbits for ROM.

The CPU can be done in 1160 2-input Nand gates. In CMOS, each Nand requires 4 transistors.

An actual CMOS implementation could take advantage of other logical gate types, and transmission gates, to substantially reduce the transistor count.

--Mark

To unsubscribe from How many transistors would a physical implementation of the Jack computer require?, click here.

NAML

|

|

|

Perhaps slightly off-topic, but I've been poking at a game called MHRD that covers a lot of the same principles... but it also encourages NAND-perfection by automatically counting the NANDs for you in each of your chips and comparing to the global record. (It's what inspired me to make a 4-NAND DMux, 5-NAND HalfAdder, and 9-NAND FullAdder).

I'll try to work-out what I've got going (so far) in my current chipset (and it may illustrate why using the builtin chips becomes necessary after you have a larger chipset... Assuming I'm doing my math correctly... Feel free to call me on any errors....)

If the DFF is basically 2 NAND gates... My Mux can probably be improved but right now is two And, two Or, and a Not for 11 NAND (total 13 per Bit)... a register uses 16 Bits, (so we're [okay, maybe just me] at 208 NAND) for a 16-Bit Register with my chip designs.... Eight of those (total 1664 NAND) plus, per my design one DMux8Way (36 more NAND with my optimized design) and one Mux8Way16 (176 NAND in Mux16, seven in my Mux8Way16 for +1232... our grand total of my design for RAM8 = 1232 + 36 + 1664 = 2932 NAND...)

RAM64 then = 1232 + 36 + (8 * 2932) NAND in my chipset.... or 24,724 NAND....

extrapolating, ~x8 for 512kb ~50,000 NAND...

...and ~x8 for 4096kb ~400,000 NAND...

...and ~x4 for 16Kb = ~1,600,000 NAND just for the main memory.

> 3 million inputs, nearly 5 million I/O lines in total.

Then again, maybe I've mis-managed my calculations... this amazing feat is comprised of ~43,000 transistors (obviously using more optimal gates where possible, but it still makes me doubt my strikingly different calculations....) Check it out: The Megaprocessor

|

|

|

Okay, that terrible Mux design just had to go.... I don't know why I didn't optimize it further sooner, but the reality of those NAND #'s for memory forced me to act. :) Optimizing my Mux to a 4-NAND design means 6 in a Bit, 96+36+28 in a register (160; down 48 from what I calculated as 208 with the prior Mux chip).

So.... there will still be a "really big" # of NAND to simulate in the entire finished HACK computer.

... 10,812 NAND for RAM64 ....

And apparently I did make an error in the prior calculations... in the conservative direction, though, surprisingly enough. Because my new calculation, for my optimized design, has 2.7 million NAND.... nearly twice as many as I calculated for my less efficient design. And again, that's just the NANDs in the 16Kb of main memory.

Bottom line? Lots and lots and lots of gates.... :)

|

|

|

Thank you for the clarification and additional information!

|

|

Administrator

|

You might also be interested in Logisim. It's a fairly powerful schematic based logic simulator.

http://www.cburch.com/logisim/ It is good enough to simulate a Hack-like computer. See this post for an example.

--Mark

|

|

|

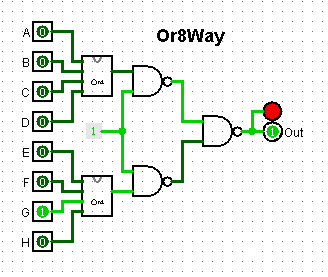

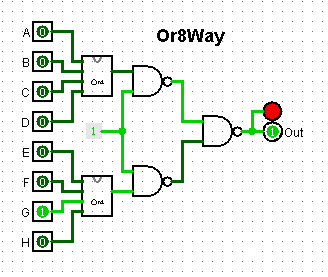

Fantastic! I don't think I could have asked for more! I had been looking at tools like DIA, Multimedia Logic, and TinyCAD to help me visualize the circuits I've been working on. This is definitely next-level. Today I've created my 2-gate-NAND foundation of circuits:

Mux,

DMux,

HalfAdder,

FullAdder,

Or3Way,

Or4Way,

Bit,

Are all now built in LogiSim, as well as the next tier that I've completed so far:

Mux16,

Add16,

Inc16,

Register16b,

Or8Way,

Not16

It's been fun and interesting learning to do these in LogiSim. One project I have at-hand is my 1st PCounter. Being able to draft it here now in LogiSim with my own prefabs should help me wrap my head around it, I think. At the very least, I'll be going through much less paper now, so thanks again! (I note that screenshots of these are also far cleaner than my pen and paper doodles....)

|

|

|

I'm about to start this course and was curious if I could/should actually make the circuits on a breadboard, and if I'd want to do so, is there a guide for that?

Thanks

|

|

|

I would not discourage you from attempting to breadboard some of these circuits; it should be a fun, interesting and rewarding experience. I used LogiSim which is basically a virtual breadboard, which has a few advantages: 1) no mess, 2) no investment in parts, 3) no workspace needed, 4) quicker assembly, 5) ability to use your own custom "chips" as components, 6) leading to the ability to "produce" thousands of gates in short order.

Either way, good luck!

|

|

Administrator

|

I would NOT recommend physically building this using NAND gates. While it would undoubtedly be interesting to do, it would be rather expensive and would primarily be an exercise in tracking down and fixing the inevitable large number of wiring errors and poor connections that will result.

If you really want to build something up in hardware I would recommend a tiered approach, similar to the projects themselves. Build the primitive gates using NAND gates, then use off-the-shelf primitive gates to build the next level up, then use off-the-shelf versions of those to build the next level, and so on. At each stage you have confidence that you could implement the entire thing with nothing but NAND gates if you really had to.

Another thing to keep in mind is that the notion of building a computer from NAND gates alone is fine conceptually, but it is not how it would ever be done in reality. Even just considering the basic gates, we do not use a NAND gate (four transistors in CMOS) to make an inverter (NOT gate), we use two transistors to make an inverter directly. To really show how inefficient this approach would be, consider a NOR gates. Using NAND gates alone we would use four of them (sixteen transistors) when we can just use the same four transistors that are in a single NAND gate, wire them up just slightly differently, and have a NOR gate.

|

|

|

Jack Draak wrote

I used LogiSim which is basically a virtual breadboard

And if you go with LogiSim you can use this wonderful display with your HACK computer (disclosure: shameless self-promotion).

|

|