I need help,sir

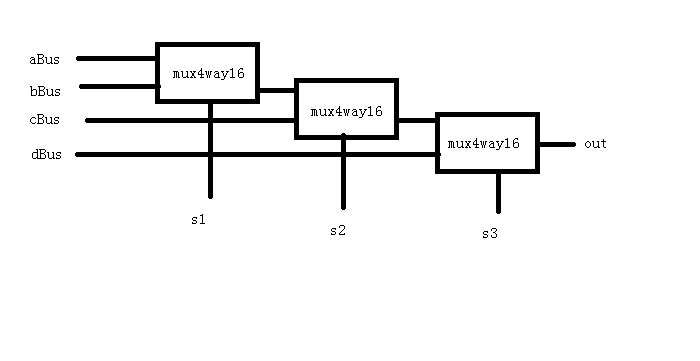

by using Mux16 to implement the Mux4way16 chip,i figure out this construction:

but this will cause an internal bus problem

one of my HDL code is:

Mux16(a=a[0..15], b=b[0..15], sel=s1, out[0..15]=o1[0..15]);

syntax problem in out[0..15]=o1[0..15]

by the way, why is Hack HDL not able to assign internal buses?

i think it will be more convenient for readers to implement complex chip with internal buses.