Hello all,

I've been alright with everything so far up until this chip. It is failing at line 7 and 8 - comparison error.

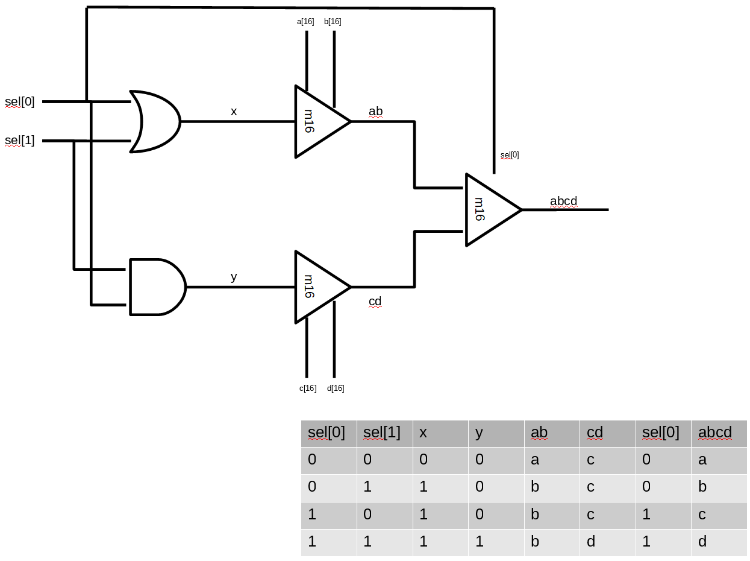

Here is a drawing to show my idea. I can also email my HDL that fails if someone would be so kind as to see if I screwed up that.

I was sneaky after working on this problem for so long and look at a solution, but the solution just seemed too easy it must be wrong?

Is my thinking correct?Thank you :)