I have been stuck on trying to break down the implementation of the CPU. This probably stems from a lack of understanding.

I have tried cadet's advice on printing out several copies of the CPU diagram and taking notes on them to try to understand it but am still not really sure where to go from here.

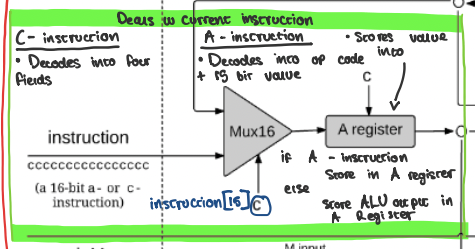

What I think I understand so far is that in the case of a C-instruction (MSB == 1), the d bits are used to determine which registers accept the ALU output, the j bits are used to determine which instruction to fetch next, the ALU output is loaded into the A register, and the six c bits of the instruction are used to compute the calculation to be executed by the CPU and the a-bit determines wether the ALU will be fed the output from the A-register or the inM input. In the case of a A-instruction the instruction is loaded into the A-register.

I have watched part of Simon Schockens video on it <nabble_embed>https://www.youtube.com/watch?v=OXK_vzk7cUU&list=PLrDd_kMiAuNmSb-CKWQqq9oBFN_KNMTaI&index=38</nabble_embed> and have drawn the image above to try to break down the section which decodes and deals with the current instruction.

I could use some guidance on how to break this down into small, managable steps or just some guidance since I assume my understanding is incorrect.