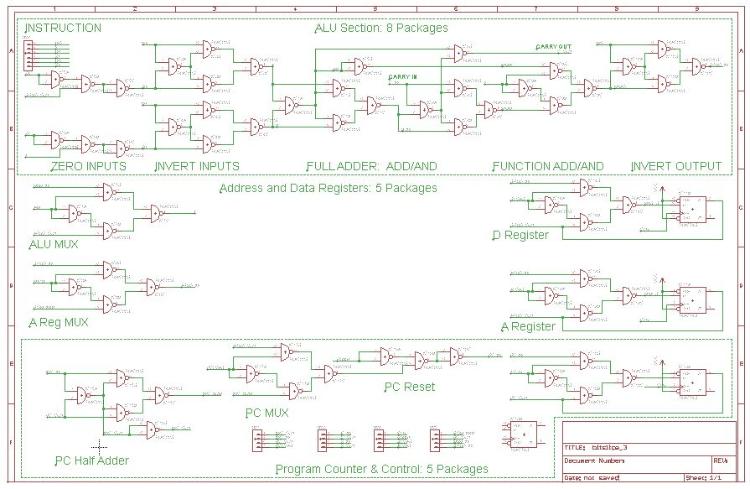

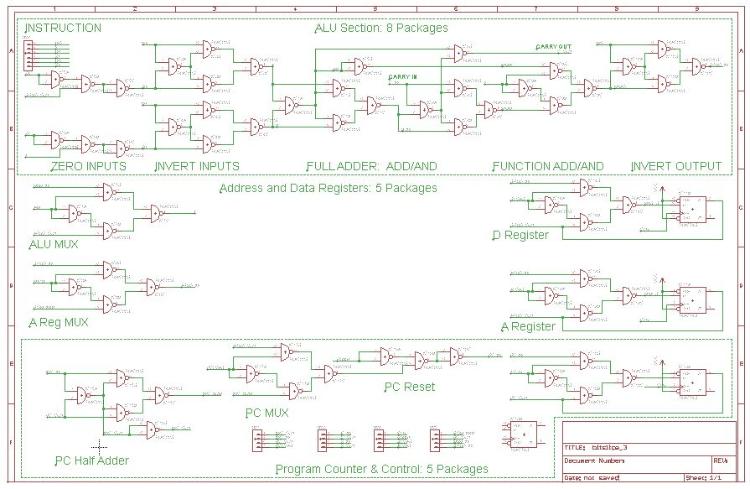

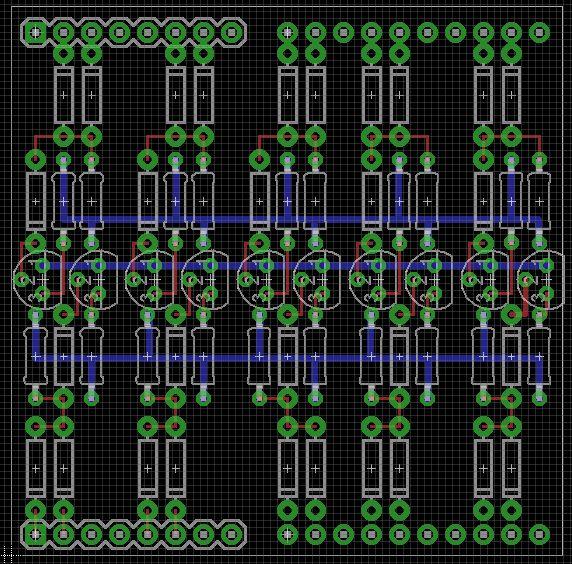

Here is the Bitslice Design. There are 16 of these connected to a common backplane that carries Address Data and instruction signals.

For convenience, the logic has been grouped into conventional TTL packages eg 74HC00 NAND gates. That allows an easy assessment to be made of how big this thing is. Whilst it could be implemented in 74HC00 logic, it could equally well be implemented in discrete DTL or on a FPGA (though bitslice would probably not be appropriate for a FPGA implementation).

The ALU has two inputs X (Dreg Out) and Y (A reg or Memory) and a Carry In bit. The Carry In connects to the Carry out from the previous slice, or if Slice 0, the Carry In is connected to zero.

The 6 Instruction inputs also connect to the ALU.

ZX Zero X

NX Invert X

ZY Zero Y

NY Invert Y

F Function (select ADD or AND function)

NO Invert Output

The ALU slice produces a single bit output that goes to the input bit of the D Register, and also a Carry Out.

Every slice performs exactly the same ALU operation given it's Xn, Yn and Cn inputs.

Address and Data Registers

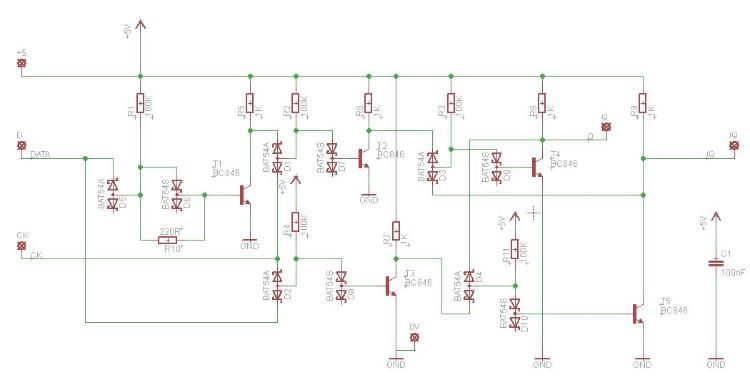

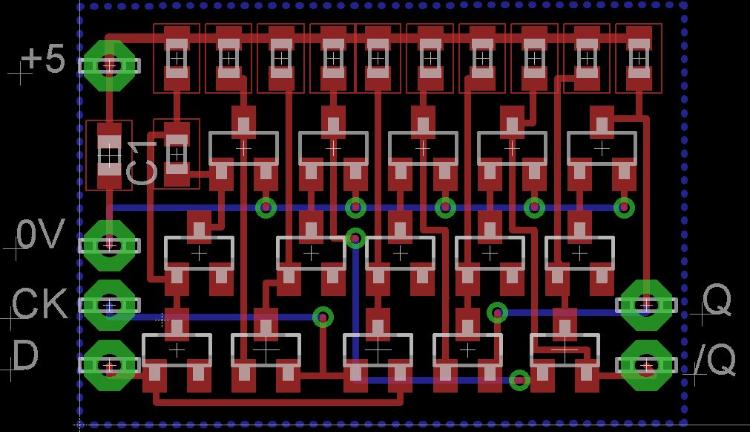

These are identical structures made from a 2 input multiplexer stage and a DFF.

Program Counter

This is somewhat more complicated, as it consists of a half-adder, a register, and the means to reset the register or load it from either the output of the A register or from an incremented version of itself.

A half adder allows the PC to be incremented by 1. (If this were extended to a full adder, the PC could jump automatically to a given address. Instead this jump address has to be supplied from the Address Register).

As can be seen, the whole slice is made from just 5 types of circuit configuration:

1. Half Adder HA

2. 2 Input MUX MX

3. Zeroer Z

4. Negater N

5. DFF D

The structure of these elements when expressed in NAND gates is remarkably similar, a zeroer is just a special case of a 2 input MUX that can select between zero or the data input, a Negater is very similar to a half-adder in appearance, and will invert the input bit depending on the control input NX. It's actually an Exclusive OR made from 4 NAND gates, just like the half-adder.

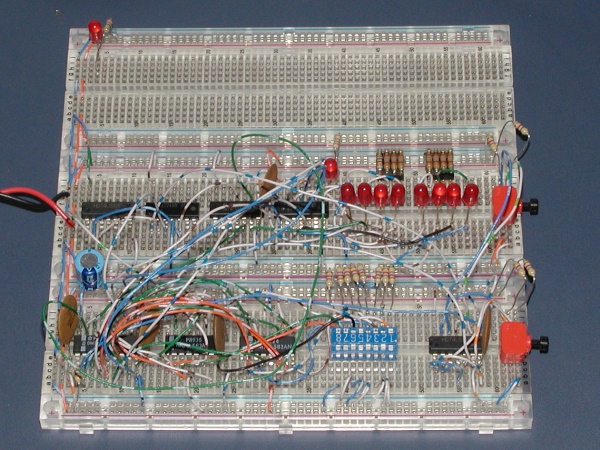

If these elements can be implemented efficiently in logic, whether DTL, TTL, CMOS etc, and be shown to work at high speed without glitches, then just about any computer architecture may be built up from them. It's like having a LEGO set with 5 different colours of blocks. DTL will run at about 2MHz maximum, and my DFF design needs more tuning of resistor values to get it to clock at much more than 200kHz.

As stated earlier the carry propagation delay through 16 slices (both for the ALU and the PC) can be significant - and this will limit the overall speed that a DTL version of Hack will run at.