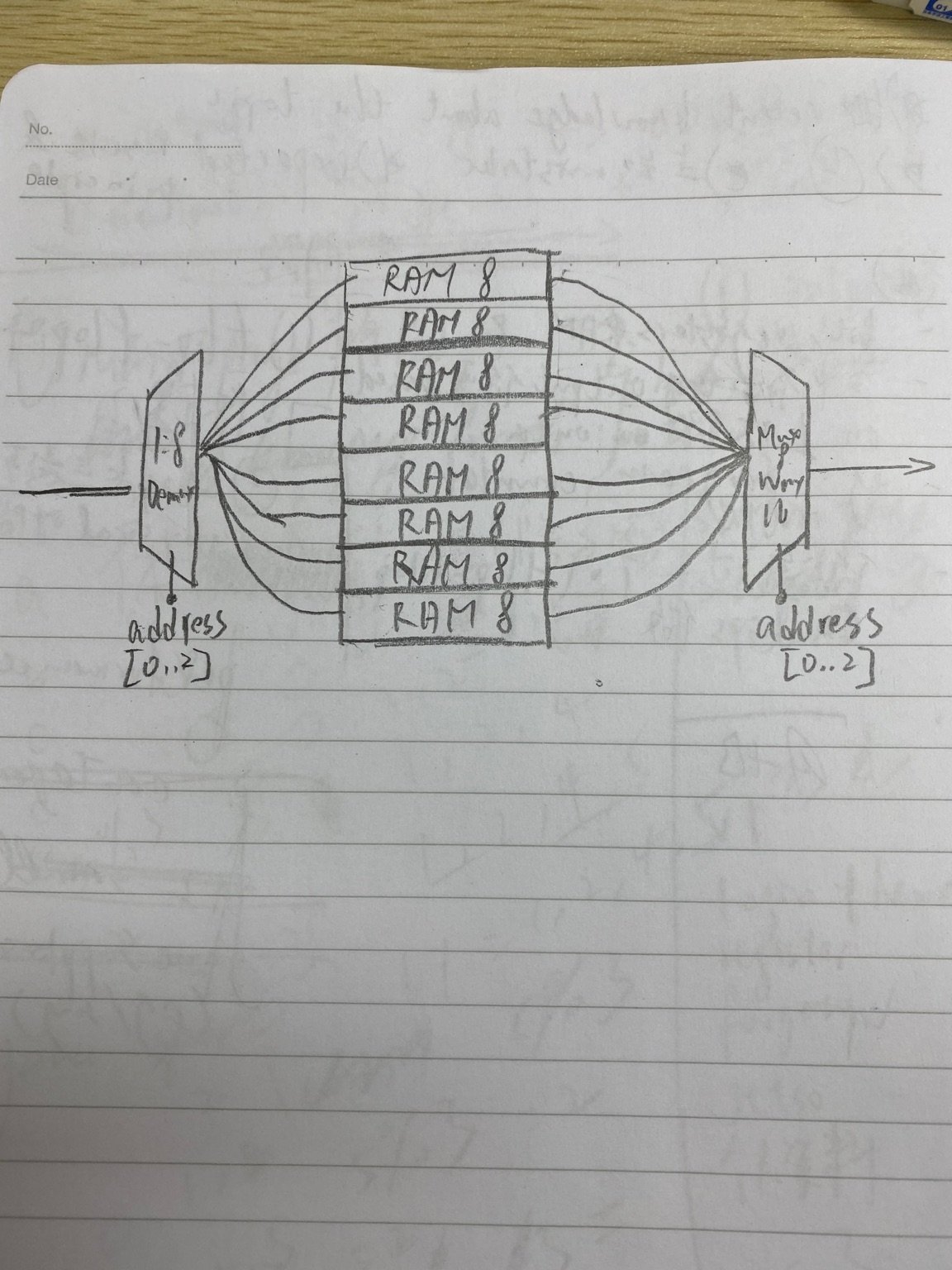

In the diagram I draw, for the demultiplexer and the multiplexer. The same bits of address need to be passed in. However, the remaining bits of address need to be be passed to EACH RAM8 as well.

What I would like to ask is that are those address bits are being passed to the suitable place at the same time?